# **Electric Stress-Induced Threshold** Voltage Instability of Multilayer MoS<sub>2</sub> **Field Effect Transistors**

Kyungjune Cho,<sup>†</sup> Woanseo Park,<sup>†</sup> Juhun Park,<sup>†</sup> Hyunhak Jeong,<sup>†</sup> Jingon Jang,<sup>†</sup> Tae-Young Kim,<sup>†</sup> Woong-Ki Hong, \*, \* Seunghun Hong, \*, § and Takhee Lee\*, \*

<sup>†</sup>Department of Physics and Astronomy, Seoul National University, Gwanak-ro, Gwanak-qu, Seoul 151-744, Korea, <sup>‡</sup>Jeonju Center, Korea Basic Science Institute, Jeonju, Jeollabuk-do 561-180, Korea, and Speartment of Biophysics and Chemical Biology, Seoul National University, Gwanak-ro, Gwanak-gu, Seoul 151-747, Korea

**ABSTRACT** We investigated the gate bias stress effects of multilayered MoS<sub>2</sub> field effect transistors (FETs) with a back-gated configuration. The electrical stability of the MoS2 FETs can be significantly influenced by the electrical stress type, relative sweep rate, and stress time in an ambient environment. Specifically, when a positive gate bias stress was applied to the MoS<sub>2</sub> FET, the current of the device decreased and its threshold shifted in the positive gate bias direction. In contrast, with a negative gate bias stress, the current of the device increased and the threshold shifted in the

negative gate bias direction. The gate bias stress effects were enhanced when a gate bias was applied for a longer time or when a slower sweep rate was used. These phenomena can be explained by the charge trapping due to the adsorption or desorption of oxygen and/or water on the MoS<sub>2</sub> surface with a positive or negative gate bias, respectively, under an ambient environment. This study will be helpful in understanding the electrical-stress-induced instability of the MoS<sub>2</sub>-based electronic devices and will also give insight into the design of desirable devices for electronics applications.

KEYWORDS: molybdenum disulfide · field effect transistor · electronic transport · gate bias stress

wo-dimensional (2D) nanomaterials with layered structures, such as graphene, are of considerable interest as promising materials for next-generation nanoelectronic device applications because of their unique properties and the ability to easily fabricate complex structures. 1,2 Among the layered materials, molybdenum disulfide (MoS<sub>2</sub>) has recently attracted a lot of attention due to its intriguing electrical and optical properties compared to the substantial limitations of graphene in electronic transistors.3,4

Unlike graphene, which does not have a band gap, bulk MoS2 is a semiconductor with an indirect band gap of 1.2 eV, and single-layer MoS<sub>2</sub> is a semiconductor with a direct band gap of 1.8 eV.<sup>5,6</sup> Furthermore, MoS<sub>2</sub> has other excellent characteristics such as optical sensitivity and mechanical flexibility.<sup>7–10</sup> Accordingly, there have been considerable efforts into fabrication and characterization of MoS2-based field effect transistors (FETs), sensing devices, memory

devices, and logic circuits for future electronics and optoelectronics.4,11-18 For example, single-layer MoS<sub>2</sub> transistors with a high on/off ratio of 108 have recently been demonstrated using HfO2 as the top gate dielectric.4 Additionally, multilayer MoS<sub>2</sub> transistors exhibiting high mobility (>100 cm<sup>2</sup>/(V s)), near-ideal subthreshold swing ( $\sim$ 70 mV/decade), and robust current saturation over a large voltage window have also been demonstrated.<sup>18</sup>

Despite these merits, large variations in the transport properties of MoS<sub>2</sub> FET devices due to extrinsic effects, such as absorption of oxygen and/or water from the environment, can result in limitations for exploring their intrinsic properties and overall stability. 19-22 Very recently, Late et al. showed that the hysteresis effects of MoS<sub>2</sub> FET devices measured under an ambient environment were presumably due to extrinsic/environmental effects, especially absorption of moisture on the surface.<sup>21</sup> Qiu et al. showed that because the MoS2

Received for review May 10, 2013 and accepted August 7, 2013.

Published online August 08, 2013 10.1021/nn402348r

© 2013 American Chemical Society

<sup>\*</sup> Address correspondence to (W.-K.H) wkh27@kbsi.re.kr: (T.L) tlee@snu.ac.kr.

FET devices were sensitive to oxygen in the ambient environment, exposure to ambient conditions dramatically reduced the on-state current due to the additional scattering centers at the defect sites of MoS<sub>2</sub> caused by chemisorption.<sup>22</sup> They also demonstrated that vacuum annealing could effectively remove the adsorbates and reversibly recover the FET device performance.<sup>22</sup> Although there have been a number of reports on MoS<sub>2</sub> FET devices, the FET device stability under electrical stress has not yet been fully investigated. Understanding the electrical-stress-induced stability is very important in MoS<sub>2</sub>-based FETs for developing appropriate device operation schemes for use in practical electronic devices.

Here, we investigated the electrical-stress-induced instability of multilayered  $MoS_2$  FETs with a back-gated configuration under ambient conditions. For example, we studied the device's characteristics in response to a positive or negative gate bias stress ( $\pm 35$  V). The current of the device decreased (increased) and its threshold shifted in the positive (negative) gate bias stress. We also studied the device's characteristics with different gate bias stress times, different gate bias sweep rates, and different gate sweep ranges. We compared the gate bias stress effects of the device in the ambient environment and in a vacuum.

## **RESULTS AND DISCUSSION**

The MoS<sub>2</sub> flakes used in this study were prepared by the micromechanical exfoliation of a bulk MoS2 crystal (purchased from SPI Supplies, USA). The exfoliated MoS<sub>2</sub> flakes were transferred to a 100-nm-thick SiO<sub>2</sub> layer on a highly doped p++ Si substrate that can be used as a back gate. After the MoS<sub>2</sub> flakes were transferred to the substrate, we located a suitable MoS<sub>2</sub> nanosheet that was a few layers thick using an optical microscope (see the atomic force microscope (AFM) image and cross-sectional profile in the Supporting Information, Figure S2). Then, to fabricate a MoS<sub>2</sub> FET device, the MoS<sub>2</sub> nanosheet was patterned using electron beam lithography. After patterning, Au (100-nm-thick)/Ti (10-nm-thick) was deposited as the source and drain electrodes using an electron beam evaporator. Using these methods, we made three MoS<sub>2</sub> FET devices. However, for the systematic study and comparison, all the data presented in this study were from one device. Detailed information of the device fabrication is explained in the Methods and Supporting Information

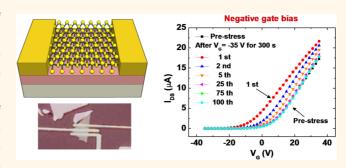

Figure 1(a) shows a schematic of a  $MoS_2$  FET with an optical image of the real device used in this study. Figure 1(b) displays the representative transfer characteristics (source—drain current *versus* gate voltage,  $I_{DS}-V_G$ ) measured at a fixed source—drain voltage ( $V_{DS}=0.1$  V). The inset of Figure 1(b) shows the output characteristics (source—drain current *versus* source—drain

Figure 1. (a) Schematic of the  $MoS_2$  FET. An optical image of a real device is also shown. (b)  $I_{DS}-V_G$  curve measured at a fixed  $V_{DS}=0.1$  V in a vacuum. The inset shows  $I_{DS}-V_{DS}$  for different  $V_G$ .

voltage,  $I_{DS}$ – $V_{DS}$ ) measured at different gate voltages  $(V_G = 10, 5, 0, \text{ and } -5 \text{ V})$ . These data were measured in a vacuum ( $\sim$ 5.6  $\times$  10<sup>-5</sup> Torr). The device exhibited n-channel FET behavior because positive gate voltages increased the current. From the transfer characteristics (Figure 1(b)), we estimated a field effect mobility ( $\mu$ ) of  $\sim$ 25.7 cm<sup>2</sup>/(V s) using the following formula,  $\mu = [dI_{DS}/$  $\mathrm{d}V_\mathrm{G}] \times [L/(WC_\mathrm{i}V_\mathrm{DS})],^{23}$  where  $W=6.3~\mu\mathrm{m}$  is the channel width,  $L = 0.9 \,\mu\text{m}$  is the channel length, and  $C_i = \varepsilon_o \varepsilon_r / d \approx$  $3.5 \times 10^{-4}$  F/m<sup>2</sup> is the capacitance between the active layer and the back gate per unit area. Here,  $\varepsilon_{\rm r}$  is the dielectric constant of SiO<sub>2</sub> ( $\sim$ 3.9),  $\varepsilon_0$  is the vacuum permittivity, and d is the  $SiO_2$  thickness (100 nm). Previous studies have reported that the mobility of single-layer MoS<sub>2</sub> FETs is in the range from 0.1 to  $\sim$ 200 cm $^2$ /(V s). $^{4,18,19,24,25}$

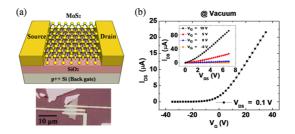

We investigated the threshold voltage instability for the MoS<sub>2</sub> FET device under various gate bias stresses. To investigate the effect of the gate bias stress on the electronic properties of the device, we first applied a constant gate bias for 300 s, and then we measured 100 transfer characteristic curves consecutively. Figure 2(a,b) display these repeated measurement results. First, the data were obtained (black curve, denoted as "pre-stress"), then a constant +35 V (Figure 2(a)) or -35 V(Figure 2(b)) gate bias stress was applied for 300 s, and finally, 100 consecutive data points were measured. After the positive gate bias stress, the source-drain current decreased significantly and the threshold voltage of the device shifted in the positive gate bias direction (see the data labeled "1st" in Figure 2(a)). Then, the current gradually increased and the threshold voltage shifted in the negative gate bias direction, and eventually, the curve approached the original state (pre-stress curve). In contrast, for the negative gate bias stress, the current increased and the threshold voltage shifted in the negative gate bias direction (see the data labeled "1st" in Figure 2(b)). Then, the current gradually decreased and the threshold voltage shifted in the positive gate bias direction, and similar to the positive gate bias stress, the curve returned to the original state (pre-stress curve). Figure 2(c) shows the shift in the threshold voltage at each measurement with respect to the value for the pre-stress curve. Here, the threshold voltage is the value

Figure 2. (a, b)  $I_{DS}-V_G$  curves ("pre-stress") measured before the gate bias stress and 100 consecutive  $I_{DS}-V_G$  curves right after (a) +35 V gate bias stress and (b) -35 V gate bias stress was applied for 300 s. Data were measured in ambient conditions. (c) Shift of the threshold voltage ( $\Delta V_{Th}$ ) for each measurement with respect to the value of the pre-stress curve.

of the gate bias when the channel just begins to allow significant current to flow; we determined the threshold voltage from the x (gate voltage)-axis intercept obtained from the linear fitting of the linear parts of the characteristic transfer curves. <sup>23,26</sup> With  $V_{\rm Th}$  determined, we also estimated the carrier density of the device (see details in Figure S5 in the Supporting Information).

These phenomena (Figure 2) can be attributed to charge trapping due to the adsorption of oxygen and/ or water in an ambient environment at defect sites on the MoS<sub>2</sub> surface. 19,20,22 Charge trapping under a positive gate bias stress can be enhanced by an increase in the adsorption of oxygen and/or water at the MoS<sub>2</sub> channel surface due to the increase in electrons caused by the positive gate bias. The charge trapping results in a decrease in the electrical conductance and causes the threshold voltage shifts in the positive gate bias direction. The electrons trapped on the MoS<sub>2</sub> surface can be released by applying a negative gate bias, which results in an increase in the conductance, and the threshold voltage shifts toward the negative gate bias direction. Similar behaviors have been observed in other types of nanoelectronic devices made with ZnO nanowires, InGaZnO(IGZO) films, and graphene.<sup>27–33</sup> Unlike such materials-based FETs, the threshold voltage instability in Si-based FETs can be explained mainly in terms of defect state creation and charge trapping effect at the interface between channel layer and dielectric layer under electrical stresses.<sup>34–36</sup> In our experiments, the adsorption/desorption of oxygen and water molecules on the MoS<sub>2</sub> surface under ambient environment starts to play dominant roles in the electrical transport properties of MoS<sub>2</sub> FETs.

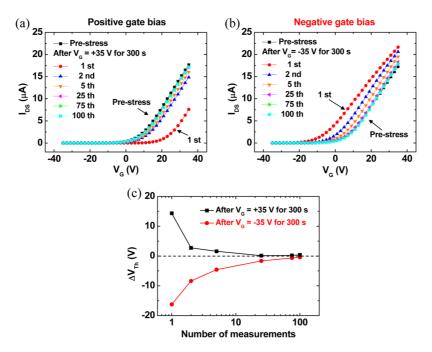

We also investigated the effect of the gate bias stress time on the same device in ambient conditions. Figure 3(a) presents the transfer characteristic data (at  $V_{DS} = 0.1$  V) of the device obtained right after we applied a constant +35 V gate bias for different gate bias stress times that varied from 0 to 500 s with a fixed gate bias sweep rate of 8 V/s. The inset of Figure 3(a) shows the logarithmic plot. For example, the data labeled "10 s" were obtained after we applied a +35 V gate bias for 10 s. We waited about an hour before each measurement to ensure that the device fully recovered from the previous gate bias stress. We confirmed that the data were fully recovered; in other words, the measured data were almost the same after waiting an hour for all gate bias stresses. Please see the two "0 s" curves in Figure 3(a,b), which are very similar because the waiting time was sufficient for the device to fully recover. From Figure 3(a), one can see that under a positive gate bias stress the current decreased and the threshold voltage shifted in the positive gate bias direction.

We repeated the gate bias stress measurements with a negative gate bias. Figure 3(b) displays the transfer characteristics data obtained after we applied a constant —35 V gate bias for different times while all the other conditions were the same as in Figure 3(a). For the negative gate bias stress (Figure 3(b)), the current increased and the threshold voltage shifted in the negative gate bias direction. The results in Figure 3 are consistent with the observed results in Figure 2: a positive (negative) gate bias stress decreased (increased) the current and the threshold voltage shifted in the positive (negative) gate bias direction. These observations are

Figure 3. (a, b)  $I_{\rm DS}-V_{\rm G}$  curves measured in ambient conditions after (a) +35 V and (b) -35 V gate bias stress was applied for different stress duration times. (c) Shift in the threshold voltage ( $\Delta V_{\rm Th}$ ) for each measurement with respect to the value for the initial curve ("0 s" curve). The inset is the plot made on the logarithmic scale of stress time.

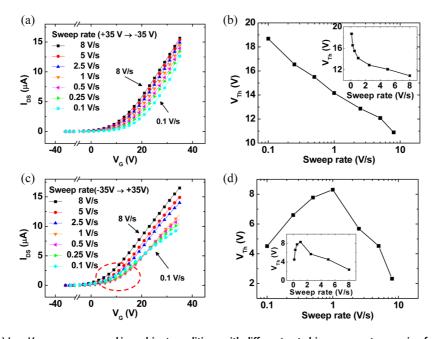

Figure 4. (a, c)  $I_{DS}-V_G$  curves measured in ambient conditions with different gate bias sweep rates ranging from 8 to 0.1 V/s. The gate bias was swept (a) from +35 to -35 V and (c) from -35 to +35 V. (b, d) Threshold voltage ( $V_{Th}$ ) at each measurement for different sweep rates for gate bias swept (b) from +35 to -35 V and (d) from -35 to +35 V. Insets in (b) and (d) are plots made as the linear scale of sweep rate.

due to the charge trapping associated with the ambient effect. The shift in the threshold voltages at each measurement as a function of the gate bias stress time for both the positive and negative gate biases was plotted in Figure 3(c). The inset in Figure 3(c) is the logarithm time scale. One can see that the shift in the threshold voltage increased with respect to the value for initial curve (0 s) as the gate bias stress time increased for both gate bias polarities. When the gate bias is applied for a long enough duration, the absorbed oxygen and/or water will

be saturated and the shift in the threshold voltage will also be saturated.

We also examined the effect of the gate bias sweep rate on the device's characteristics. Figure 4(a) shows the transfer characteristics measured at ambient conditions with a gate bias sweep from +35 V to -35 V at different sweep rates (from a fast rate of 8 V/s to a slow rate of 0.1 V/s). As shown in Figure 4(a), as the sweep rate decreased, the current decreased, and the threshold voltage shifted in the positive gate bias direction.

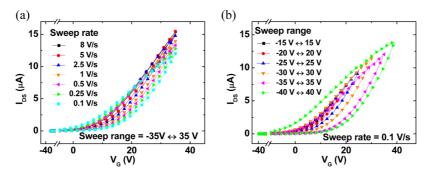

Figure 5. (a) Hysteresis  $I_{DS}-V_G$  curves of double sweep (from -35 to +35 V and then back to -35 V) at different gate bias sweep rates measured in the ambient environment. (b) Hysteresis  $I_{DS}-V_G$  curves with different gate bias sweep range at a fixed gate bias sweep rate of 0.1 V/s in ambient.

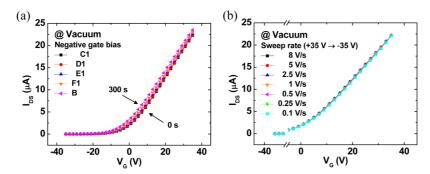

Figure 6. (a)  $I_{DS}-V_G$  curves measured in a vacuum after -35 V gate bias stress was applied for different stress duration times. (b)  $I_{DS}-V_G$  curves measured in a vacuum during the gate bias sweep from +35 to -35 V with different gate bias sweep rates.

The positive shift of the threshold voltage as the sweep rate decreased can be observed in the logarithmic scale (Figure 4(b)) and linear-scale plot (Figure 4(b) inset). This behavior is consistent with the data in Figures 2(a) and 3(a) because a slow sweep rate means a longer gate bias stress time. Similar behavior was observed in the case of the opposite gate bias sweep direction (i.e., the sweep from -35 V to +35 V with the same sweep rate conditions), as shown in Figure 4(c,d). As the sweep rate decreased, the current also decreased, and the threshold voltage shifted in the positive gate bias direction as a result of the longer stress time of the positive gate bias at the slower sweep rates. However, at the slower sweep rates of 0.5, 0.25, and 0.1 V/s, the current first increased around a low gate bias (circled in Figure 4(c)), then it decreased at larger positive gate bias. This can be explained by considering the positive and negative gate bias sweep ranges separately; at slower rates, when the gate bias was swept from -35 to 0 V, the current tended to increase first (consistent with the case of Figures 2(b) and 3(b)), and then when the gate bias was continuously swept from 0 V to +35 V, the current decreased (consistent with the case of Figures 2(a) and 3(a)). This phenomenon resulted in an increase and then decrease in the threshold voltage as the sweep rate slowed (from 8 V/s to 0.1 V/s), as shown in Figure 4(d).

Figure 5 displays the effect of gate bias double sweeps, *i.e.*, -35 to +35 V and then back to -35 V, at the same sweep rates. The results are shown in Figure 5(a). As the

sweep rate decreased, the current tended to increase in the negative gate bias range (-35 to 0 V) and to decrease during the positive gate bias range (0 to +35 V); thus, there is a hysteresis in the double sweep loop. This hysteresis effect became more obvious at the slower sweep rates because the slower sweep rates (*i.e.*, longer gate bias time) enhanced the gate bias stress effects. Similarly, this hysteresis effect became more significant as the gate bias sweep range increased (Figure 4(b)).

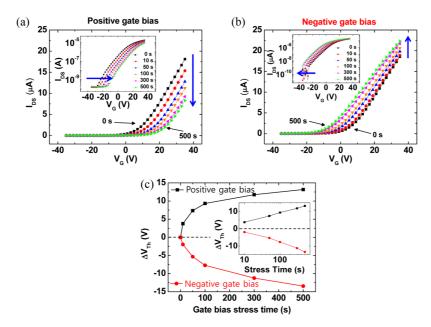

To investigate the ambient effect, we repeated the gate bias stress measurements in a vacuum (5.6  $\times$   $10^{-5}$  Torr). Figure 6(a) shows the transfer characteristic curves that were measured in a vacuum with the same measurement conditions as the data in Figure 3(b). Figure 6(b) shows the data measured in a vacuum at the same conditions as the data in Figure 4(a). No significant gate bias stress effects were observed in the vacuum environment. There were small shifts observed in the data, especially in Figure 6(a). These shifts are due to the interfacial traps at the interface between the MoS $_2$  and SiO $_2$  dielectric layer in response to the gate bias stress.

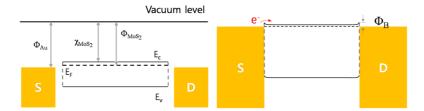

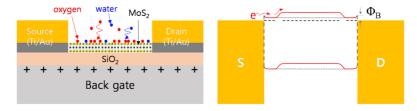

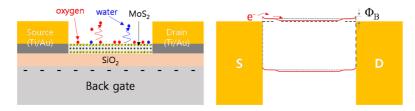

Next, we discuss the gate bias stress effect on the  $MoS_2$  FET using energy band diagram schematics. Figure 7 shows the energy band diagram for  $V_{SD} = 0$  V and  $V_G = 0$  V at ambient conditions for three cases: no gate bias stress, positive gate bias stress, and negative gate bias stress. To understand the charge transport, we need to consider the metal/ $MoS_2$  contact interfaces at the source and drain electrodes because metal contacts to semiconducting  $MoS_2$  can create

#### (a) No gate bias stress

(b) Positive gate bias stress (oxygen and water adsorption)

(c) Negative gate bias stress (oxygen and water desorption)

Figure 7. Schematics of the energy band diagram at  $V_G = 0$  V in the ambient environment when (a) no gate bias stress, (b) positive gate bias stress, and (c) negative gate bias stress is applied.

Schottky barriers, which can dominate the electronic properties of MoS<sub>2</sub>-based devices. We first assume that although a band gap of MoS<sub>2</sub> is dependent on their thickness, our MoS<sub>2</sub> nanoflakes have a band gap of about 1.2 eV, similar to that of the bulk. In addition, MoS<sub>2</sub> has an electron affinity of 4.0 eV, <sup>37,38</sup> a work function of 4.6-4.9 eV. 39,40 Contact metals used as source and drain electrodes in our study are Ti and Au, with work functions of 3.9-4.3 and 5.1-5.4 eV, respectively. Because the Ti layer is an adhesion layer for Au contact to a MoS<sub>2</sub> nanoflake, we considered the band alignment of Au-MoS2 interfaces at the source and drain. According to Popov et al., 41 the Ti can play a role in modifying the interface properties due to an increase in the density of state at the Fermi level  $(E_F)$ , resulting in a low-resistance ohmic contact. Our results clearly indicate that the MoS<sub>2</sub> FET device exhibits the typical n-type semiconducting behavior with lowresistance ohmic contact at low voltages in the output curves (see  $I_{\rm DS}-V_{\rm DS}$ , the inset of Figure 1(b)), which is consistent with previous results. 38,39,42 Accordingly, we can consider the band alignment for the Au/MoS<sub>2</sub> contacts at the source and drain with a very small Schottky barrier ( $\Phi_B$ ), as shown in Figure 7(a). Here, we assume that the gate bias stress effects can be due to the adsorption/desorption of oxygen and water on

the MoS<sub>2</sub> surface, and the MoS<sub>2</sub> region underneath the metal contact is not affected by such adsorption/ desorption. In the case of the application of identical positive gate bias stress, the accumulated electron density in the channel region increases by positive electric field and the resulting adsorbed oxygen and water concentration on the MoS2 channel surface is also increased, in which the adsorbed oxygen and water can capture charge carriers from the conduction band in the MoS2 channel. This causes channel depletion and the observed positive  $V_{Th}$  shift (Figures 2(a) and 3(a)). As shown in Figure 7(b), carriers first travel through the interface region between the MoS<sub>2</sub> and metal contact and then traverse the channel depletion-induced conduction barrier before entering into the MoS<sub>2</sub> channel. In contrast, when a negative gate bias stress is applied, oxygen and water desorb in response to the identical negative gate electric field. The electrons that are trapped by the adsorbed oxygen and water at the MoS<sub>2</sub> channel region are released and transferred to the MoS<sub>2</sub> channel by the application of negative gate bias stress, which results in a reduction of the carrier depletion of the MoS<sub>2</sub> FET. As shown in Figure 7(c), the desorption of oxygen and water causes the accumulation of charge carriers from the conduction band in the MoS<sub>2</sub> channel, leading to the observed

negative  $V_{\text{Th}}$  shift (Figures 2(b) and 3(b)). These results suggest that the passivation of the  $\text{MoS}_2$  surface will be important to obtain reproducible results and to minimize the ambient effect.

### CONCLUSION

We investigated the electrical-stress-induced threshold voltage instability of multilayered MoS<sub>2</sub> FET devices with a back-gated configuration under an ambient environment. When a positive (negative) gate bias stress was applied to the device, the current decreased

(increased) and the threshold shifted in the positive (negative) gate bias direction. This effect was enhanced when a longer gate bias time or a slower sweep rate of the gate bias was applied. These gate bias stress effects can be explained by the charge trapping mainly due to the adsorption (desorption) of oxygen and/or water on the MoS<sub>2</sub> surface with a positive (negative) gate bias under ambient conditions. Our study has important implications for a better design of functional nanodevices based on two-dimensional layered calcogenides for wide nanoelectronic device applications.

## **METHODS**

The multilayer MoS<sub>2</sub> active layer used in this study was exfoliated using the micromechanical exfoliation method from a bulk MoS<sub>2</sub> crystal purchased from SPI Supplies. Then, the multilayer MoS<sub>2</sub> flakes were transferred from 3M Scotch tape to SiO<sub>2</sub> on a heavily doped p++ Si wafer (resistivity  $\sim$ 5 × 10<sup>-3</sup>  $\Omega$  cm) that can be used as a back gate. After finding the location of a multilayer MoS<sub>2</sub> flake using an optical microscope, the MoS<sub>2</sub> nanosheet's height was measured with a NX 10 AFM system (Park Systems). To make patterns of electrodes, we spin-coated methyl methacrylate (9% concentration in ethyl lactate) and poly(methyl methacrylate) 950K (5% concentration in anisole) at 4000 rpm. After the spin-coating of each layer, the sample was baked at 180  $^{\circ}\text{C}$  for 90 s. The electrodes were patterned using an electron beam lithography system (JSM-6510, JEOL) with a 30 kV exposure. The pattern development was performed with an methyl isobutyl ketone/isopropyl alcohol (1:3) solution with a development time of 50 s. The electrical characteristics of the device were measured using a semiconductor parameter analyzer (HP 4145B) in a probe station (JANIS model ST-500).

Conflict of Interest: The authors declare no competing financial interest.

Supporting Information Available: Additional information including device fabrication details, AFM and optical images, effect of gate bias stress on the device under vacuum, and estimation of the carrier concentration. This material is available free of charge via the Internet at http://pubs.acs.org.

Acknowledgment. The authors appreciate the financial support from the National Creative Research Laboratory Program (Grant No. 2012026372) and the National Core Research Center (Grant No. R15-2008-006-03002-0) by the National Research Foundation of Korea (NRF) grant funded by the Korean Ministry of Science, ICT & Future Planning. S.H. acknowledges the support from an NRF grant (No. 2012-0000117). W.-K.H. acknowledges the financial support from a Korea Basic Science Institute (KBSI) grant (T33516).

## **REFERENCES AND NOTES**

- Novoselov, K.; Geim, A. K.; Morozov, S.; Jiang, D.; Zhang, Y.; Dubonos, S.; Grigorieva, I.; Firsov, A. Electric Field Effect in Atomically Thin Carbon Films. Science 2004, 306, 666–669.

- Novoselov, K. S.; Jiang, D.; Schedin, F.; Booth, T. J.; Khotkevich, V. V.; Morozov, S. V.; Geim, A. K. Two-Dimensional Atomic Crystals. Proc. Natl. Acad. Sci. U.S.A. 2005, 102, 10451–10453.

- Li, X.; Wang, X.; Zhang, L.; Lee, S.; Dai, H. Chemically Derived, Ultrasmooth Graphene Nanoribbon Semiconductors. Science 2008, 319, 1229–1232.

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* 2011, 6. 147–150.

- Kam, K.; Parkinson, B. Detailed Photocurrent Spectroscopy of the Semiconducting Group VIB Transition Metal Dichalcogenides. J. Phys. Chem. 1982, 86, 463–467.

- Mak, K. F.; Lee, C.; Hone, J.; Shan, J.; Heinz, T. F. Atomically Thin MoS<sub>2</sub>: A New Direct-Gap Semiconductor. *Phys. Rev. Lett.* 2010, 105, 136805.

- Bertolazzi, S.; Brivio, J.; Kis, A. Stretching and Breaking of Ultrathin MoS<sub>2</sub>. ACS Nano 2011, 5, 9703–9709.

- Castellanos-Gomez, A.; Poot, M.; Steele, G. A.; van der Zant, H. S.; Agrait, N.; Rubio-Bollinger, G. Elastic Properties of Freely Suspended MoS<sub>2</sub> Nanosheets. Adv. Mater. 2012, 24, 772–775.

- Eda, G.; Yamaguchi, H.; Voiry, D.; Fujita, T.; Chen, M.; Chhowalla, M. Photoluminescence from Chemically Exfoliated MoS<sub>2</sub>. Nano Lett. 2011, 11, 5111–5116.

- Scalise, E.; Houssa, M.; Pourtois, G.; Afanas'ev, V.; Stesmans, A. Strain-Induced Semiconductor to Metal Transition in the Two-Dimensional Honeycomb Structure of MoS<sub>2</sub>. Nano Res. 2012, 5, 43–48.

- Perkins, F. K.; Friedman, A. L.; Cobas, E.; Campbell, P. M.; Jernigan, G. G.; Jonker, B. T. Chemical Vapor Sensing with Monolayer MoS<sub>2</sub>. Nano Lett. 2013, 13, 668–673.

- Lee, H. S.; Min, S. W.; Park, M. K.; Lee, Y. T.; Jeon, P. J.; Kim, J. H.; Ryu, S.; Im, S. MoS<sub>2</sub> Nanosheets for Top-Gate Nonvolatile Memory Transistor Channel. Small 2012, 8, 3111–3115.

- Wang, H.; Yu, L.; Lee, Y. H.; Shi, Y.; Hsu, A.; Chin, M. L.; Li, L. J.; Dubey, M.; Kong, J.; Palacios, T. Integrated Circuits Based on Bilayer MoS<sub>2</sub> Transistors. *Nano Lett.* **2012**, *12*, 4674–4680

- Yin, Z.; Zeng, Z.; Liu, J.; He, Q.; Chen, P.; Zhang, H. Memory Devices Using a Mixture of MoS<sub>2</sub> and Graphene Oxide as the Active Layer. Small 2013, 9, 727–731.

- Radisavljevic, B.; Whitwick, M. B.; Kis, A. Integrated Circuits and Logic Operations Based on Single-Layer MoS<sub>2</sub>. ACS Nano 2011, 5, 9934–9938.

- Choi, W.; Cho, M. Y.; Konar, A.; Lee, J. H.; Cha, G. B.; Hong, S. C.; Kim, S.; Kim, J.; Jena, D.; Joo, J.; et al. High-Detectivity Multilayer MoS<sub>2</sub> Phototransistors with Spectral Response from Ultraviolet to Infrared. Adv. Mater. 2012, 24, 5832– 5836.

- Li, H.; Yin, Z.; He, Q.; Li, H.; Huang, X.; Lu, G.; Fam, D. W. H.; Tok, A. I. Y.; Zhang, Q.; Zhang, H. Fabrication of Single- and Multilayer MoS<sub>2</sub> Film-Based Field-Effect Transistors for Sensing NO at Room Temperature. Small 2012, 8, 63–67.

- Kim, S.; Konar, A.; Hwang, W. S.; Lee, J. H.; Lee, J.; Yang, J.; Jung, C.; Kim, H.; Yoo, J. B.; Choi, J. Y.; et al. High-Mobility and Low-Power Thin-Film Transistors Based on Multilayer MoS<sub>2</sub> Crystals. Nat. Commun. 2012, 3, 1011.

- 19. Park, W.; Park, J.; Jang, J.; Lee, H.; Jeong, H.; Cho, K.; Hong, S.; Lee, T. Oxygen Environmental and Passivation Effects on Molybdenum Disulfide Field Effect Transistors. *Nanotechnology* **2013**, *24*, 095202.

- Davis, S. M.; Carver, J. C. Oxygen Chemisorption at Defect Sites in MoS<sub>2</sub> and ReS<sub>2</sub> Basal Plane Surfaces. *Appl. Surf. Sci.* 1984, 20, 193–198.

- Late, D. J.; Liu, B.; Matte, H. S. S. R.; Dravid, V. P.; Rao, C. N. R. Hysteresis in Single-Layer MoS<sub>2</sub> Field Effect Transistors. ACS Nano 2012, 6, 5635–5641.

- 22. Qiu, H.; Pan, L.; Yao, Z.; Li, J.; Shi, Y.; Wang, X. Electrical Characterization of Back-Gated Bi-Layer MoS<sub>2</sub> Field-Effect Transistors and the Effect of Ambient on their Performances. Appl. Phys. Lett. 2012, 100, 123104.

- 23. Pierret, R. F. Semiconductor Device Fundamentals; Addison Wesley, 1996.

- Yoon, Y.; Ganapathi, K.; Salahuddin, S. How Good Can Monolayer MoS<sub>2</sub> Transistors Be? Nano Lett. 2011, 11, 3768–3773.

- Liu, H.; Neal, A. T.; Ye, P. D. Channel Length Scaling of MoS<sub>2</sub> MOSFETs. ACS Nano 2012, 6, 8563–8569.

- Arora, N. MOSFET Models for VLSI Circuit Simulation: Theory and Practice; Springer: Berlin, 1993.

- Maeng, J.; Jo, G.; Kwon, S.-S.; Song, S.; Seo, J.; Kang, S.-J.; Kim, D.-Y.; Lee, T. Effect of Gate Bias Sweep Rate on the Electronic Properties of ZnO Nanowire Field-Effect Transistors under Different Environments. Appl. Phys. Lett. 2008. 92, 233120.

- Choe, M.; Park, W.; Kang, J. W.; Jeong, S.; Hong, W. K.; Lee, B. H.; Park, S. J.; Lee, T. Investigation of Threshold Voltage Instability Induced by Gate Bias Stress in ZnO Nanowire Field Effect Transistors. *Nanotechnology* 2012, 23, 485201.

- Jeong, J. K.; Won Yang, H.; Jeong, J. H.; Mo, Y.-G.; Kim, H. D.

Origin of Threshold Voltage Instability in Indium-Gallium-Zinc Oxide Thin Film Transistors. *Appl. Phys. Lett.* 2008, 93, 123508.

- Suresh, A.; Muth, J. F. Bias Stress Stability of Indium Gallium Zinc Oxide Channel Based Transparent Thin Film Transistors. Appl. Phys. Lett. 2008, 92, 033502.

- Lee, J.-M.; Cho, I.-T.; Lee, J.-H.; Kwon, H.-I. Bias-Stress-Induced Stretched-Exponential Time Dependence of Threshold Voltage Shift in InGaZnO Thin Film Transistors. Appl. Phys. Lett. 2008, 93, 093504.

- 32. Chang, E.; Cibuzar, G.; Pande, K. Passivation of GaAs FET's with PECVD Silicon Nitride Films of Different Stress States. *IEEE Trans. Electron Devices* **1988**, *35*, 1412–1418.

- Sato, Y.; Takai, K.; Enoki, T. Electrically Controlled Adsorption of Oxygen in Bilayer Graphene Devices. *Nano Lett.* 2011, 11, 3468–3475.

- Powell, M. J. The Physics of Amorphous-Silicon Thin-Film Transistors. *IEEE Trans. Electron Devices* 1989, 36, 2753– 2763.

- Jahinuzzaman, S. M.; Sultana, A.; Sakariya, K.; Servati, P.; Nathan, A. Threshold Voltage Instability of Amorphous Silicon Thin-Film Transistors under Constant Current Stress. Appl. Phys. Lett. 2005, 87, 023502.

- Lelis, A. J; Habersat, D.; Green, R.; Ogunniyi, A.; Gurfinkel, M.; Suehle, J.; Goldsman, N. Time Dependence of Bias-Stress-Induced SiC MOSFET Threshold-Voltage Instability Measurements. IEEE Trans. Electron Devices 2008, 55, 1835– 1840.

- Han, S. W.; Kwon, H.; Kim, S. K.; Ryu, S.; Yun, W. S.; Kim, D. H.; Hwang, J. H.; Kang, J.-S.; Baik, J.; Shin, H. J.; et al. Band-Gap Transition Induced by Interlayer van der Waals Interaction in MoS<sub>2</sub>. Phys. Rev. B 2011, 84, 045409.

- Das, S.; Chen, H.-Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. Nano Lett. 2013, 13, 100–105.

- Liu, K.-K.; Zhang, W.; Lee, Y.-H.; Lin, Y.-C.; Chang, M.-T.; Su, C.-Y.; Chang, C.-S.; Li, H.; Shi, Y.; Zhang, H.; et al. Growth of Large-Area and Highly Crystalline MoS<sub>2</sub> Thin Layers on Insulating Substrates. Nano Lett. 2012, 12, 1538–1544.

- Giridharagopal, R.; Kelly, K. F. Substrate-Dependent Properties of Polydiacetylene Nanowires on Graphite and MoS<sub>2</sub>. ACS Nano 2008, 2, 1571–1580.

- 41. Popov, I.; Seifert, G.; Tománek, D. Designing Electrical Contacts to MoS<sub>2</sub> Monolayers: A Computational Study. *Phys. Rev. Lett.* **2012**, *108*, 156802.

- Ghatak, S.; Pal, A. N.; Ghosh, A. Nature of Electronic States in Atomically Thin MoS<sub>2</sub> Field-Effect Transistors. ACS Nano 2011, 5, 7707–7712.